Combinational circuit

Depends on the immediate input

Sequential Circuit

Each output depends on both present inputs and state.

Analysis Procedures

1.Label input/output

2. Obtain the functions of immediate points and output

3. Draw truth table

4. Deduce the functionality

Design methods

Gate- level design

with logic gates

Block-level design

With functional block

Main Objectives

- Reduce cost

- Increase speed

- Simple designs

Design Procedure

1. State problem

2. Determine and label the inputs and outputs of circuits

3. Draw truth table

4. Simplified boolean function

5. Draw logic diagram

Half adder

takes 2 input have 2 output

Inputsa:

X,Y

Outputs:

C - carry

S - output

Inputsa:

X,Y

Outputs:

C - carry

S - output

Full adder

We need 3 inputs, 2 outputs and one carry forward

using 2 half adders

Instead of adding 3 together, we add the pair of them together first. (first half adder)

The Z from previous and the sum added (second half adder)

=> my S

Using the carry input from the first adder or with the second carry forward from the second adder

=> my c

Looking at this, we managed to solve the problem without the use of kmaps and TT

Looking at this, we managed to solve the problem without the use of kmaps and TT

Block level design

- Decomposing the main problem to sub problems recursively

- Until sub problem small enough to be solved

4- bit Parallel Adder

Adding 2 4 bots numbers with a carry-in to produce a 5 bit result

We cannot use truth table here because there is too many variables to consider.

1. Observed each column

2. Cascading 4 full adders via their carries

=> Ripple carry

=> All input is pass in at the same time

16-bit parallel adder

=> Make use of the 4-bit parallel adder

=> Each carry out from the 4bit adder is pass to the next

4-bit adder and Subtractor

This is using 2s complement

=> Takes in a control where

s =0 , add

s= 1, subtract

Encountering subtraction:

- Convert to 1C

- Add one

We can use xor gate because not gate cannot be control

Using the control signal, xor gate will ensure

if the control is 0, the result will remain the same

if control is 1, result will flip

Thus giving us the 1 complement

Using the S to connect to the Cin, we can control the add one.

XOR gate is actually slower.

Magnitude Comparator

Compares 2 values A and B to check

Look from the MSB rightwards, comparing if the bit is 1 or 0.

If A>B:

AB' or (A'B' + A'B')......

We can use demorgan theorem to solve this problem.

At any one time, the 4 bit comparator will only have one output giving an 1 signal.

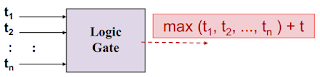

Circuit Delays:

A logic gate with delay t. If inputs are stable, then the earliest time in which the output will be stable is:

Consider a full adder circuit where all input are available at time 0

Assume each gate has delay t.

The gate will not be able to start until all input has reach

The last signal to be generated is at the MSB.

This is not practical with larger values

Faster circuits

1. Use better technology

- More expensive

- More power

- Lower level of integration

- Physical Limits

2. Use two level circuits

- Complicated design

- Product/ sum terms needs many inputs

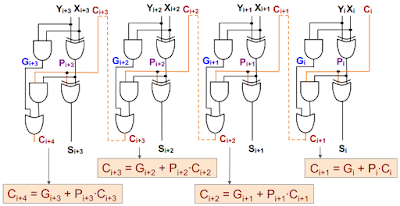

3. Look ahead techniques

- Additional cost

Carry propagate signal:

If its one, carry.

X or Y is a 1.

Carry generate signal:

Generate carry signal.

For each column, every carry depends on the propagate, generate or the previous carry signals

This will lead to long propagation delay.

- We can reduce delay by expanding and flattening the formula